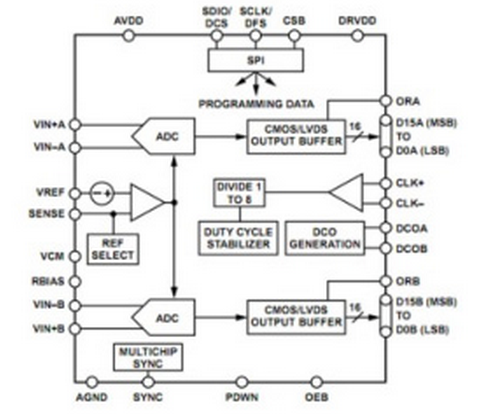

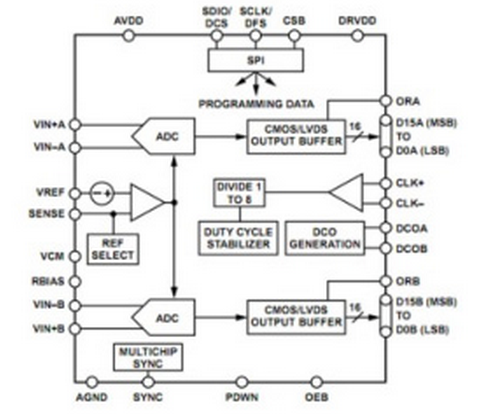

This dual channel ADC core adopts multi-level, differential pipeline architecture and integrates output error correction logic. Each ADC has a wide bandwidth, differential sample and hold analog input amplifier, which supports a variety of user selectable input ranges. The integrated reference voltage source can simplify the design. The duty cycle stabilizer can be used to compensate for the fluctuation of the ADC clock duty cycle, so that the converter can maintain excellent performance

-

[ CXAD3351 ]"

目录

7.相关产品

产品概述 返回TOP

CXAD3351是一款双通道、16位、125MSPS模数转换器(ADC).设计用来支持需要高性能、低成本小尺寸且具多功能性的通信应用。这款双通道ADC内核采用多级、差分流水线架构,并集成了输出误差校正逻辑。每个 ADC均具有宽带宽、差分采样保持模拟输入放大器,支持用户可选的各种输入范围。集成基准电压源可简化设计。占空比稳定器可用来补偿ADC时钟占空比的波动,使转换器保持出色的性能。

产品特点 返回TOP

信噪比(SNR): 78.2dBFS(70 MHz, 125MSRS)

无杂散动态范围(SFDFR): 88dBc(70MHz, 125MSPS)

低功耗:750 mW (125 MSPS)

1至8整数输入时钟分频器

中频采样频率达300 MHz

可编程ADC内部基准电压源

集成ADC采样保持输入

ADC时钟占空比稳定器

应用范围 返回TOP

分集无线电系统

多模式数字接收器(3G)

GSM. EDGE、W-CDMA, LTE、CDMA2000, WiMAX, TD-SCDMA

技术规格书(产品PDF) 返回TOP

需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持!

产品封装图 返回TOP

LFCSP-64

电路原理图 返回TOP

相关芯片选择指南 返回TOP 更多同类产品......

|

模数转换器AD converter/DA converter |

|||||||||

|

Part Number |

Function |

Resolution |

Input Voltage |

DNL |

INL |

Gain Error |

Offset Error |

Power Consumption |

Package |

|

模数转换器 |

16 Bits |

0.3~3.6 V |

-1~1.25 LSB |

±4.5 LSB |

±2.5%FSR |

±0.25%FSR |

392 mW |

LFCSP-48 |

|

|

模数转换器 |

16 Bits |

0.3~3.6 V |

±1.3 LSB |

±0.7 LSB |

±2.5%FSR |

±0.65%FSR |

777 mW |

LFCSP-64 |

|

|

数模转换器 |

16 Bits |

/ |

±2.1 LSB |

±3.7 LSB |

-3.2~4.7%FSR |

±0.001%FSR |

1815 mW |

LFCSP-72 |

|

|

数模转换器 |

14 Bits |

/ |

±0.8 LSB |

±1.3 LSB |

5.5%FSR |

/ |

1160 mW |

160-ball-BGA |

|

|

数模转换器 |

16 Bits |

/ |

±2.0 LSB |

±4.0 LSB |

±2%FSR |

±0.001%FSR |

355 mW |

LFCSP-72 |

|

|

数模转换器 |

16 Bits |

/ |

±2.0 LSB |

±4.0 LSB |

±2%FSR |

±0.001%FSR |

440 mW |

LFCSP-72 |

|

|

I/Q调制器 |

/ |

/ |

0.8 LSB |

1.3 LSB |

±10%FSR |

/ |

1800 mW |

100引脚TQFP_EP |

|