Output frequency (fQ0) is equal to reference clock oscillation (fCLKin) multiplied by N/M, within a range of 1MHz to 100MHz. Further, frequency within a range of 32kHz to 36MHz can be inputted as a reference clock. The IC stops operation when low level signal is inputted to the CE pin. For this, consumption current can be reduced and output will be one of high-impedance. Because the series is semi-custom, please ask Torex sales contacts for your requested specifications such as input/output frequency, supply voltage. However, the series has the limit of specifications; therefore, your request may not be fully satisfied with your requested frequency range.

-

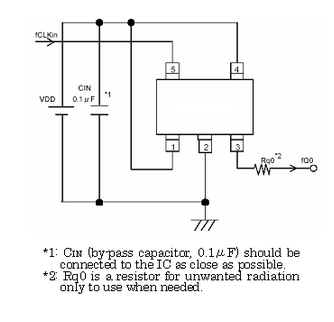

[ CXCL3471BC7 ]"

目录

7.相关产品

产品概述 返回TOP

CXCL3471BC7系列是内置分频, 倍频电路, 在整个频率范围内保持低消耗电流, 具有超小型封装的PLL时钟发生器IC。输入端分频比(M), 输出端分频比(N)的值均可以在1~256范围内通过激光微调方式自由选择。输出时钟(fQ0)的频率等于标准时钟输入频率乘以N/M的比值(即fQ0=fCLKin×N/M)。时钟输出的频率范围为:1MHz~100MHz。时钟输入频率的范围为:32kHz~36MHz。当CE端子输入低电平时,整个芯片停止工作,此时芯片的消耗电流会低于10uA。待机时输出为高阻抗。本产品提供部分客户定制品,有需要时请提供详细的规格要求(输入, 输出频率, 工作电压等)向本公司的各分公司咨询。即使在本产品的规定规格范围内,请注意有些临界范围的频率的设定可能是无法实现的。The CXCL3471BC7 series are high frequency, low power consumption PLL clock generator ICs with divider circuit & multiplier PLL circuit. Laser trimming gives the option of being able to select from input divider ratios (M) of 1 to 256 and output divider ratios (N) of 1 to 256. Output frequency (fQ0) is equal to reference clock oscillation (fCLKin) multiplied by N/M, within a range of 1MHz to 100MHz. Further, frequency within a range of 32kHz to 36MHz can be inputted as a reference clock. The IC stops operation when low level signal is inputted to the CE pin. For this, consumption current can be reduced and output will be one of high-impedance. Because the series is semi-custom, please ask Torex sales contacts for your requested specifications such as input/output frequency, supply voltage. However, the series has the limit of specifications; therefore, your request may not be fully satisfied with your requested frequency range.

产品特点 返回TOP

应用范围 返回TOP

● Clock for controlling a Imaging dot

● Microcomputer and HDD drives

● Cordless phones

● Wireless communication equipment

● PDAs

● Cameras, VCRs

● Various system clocks

技术规格书(产品PDF) 返回TOP

需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持!

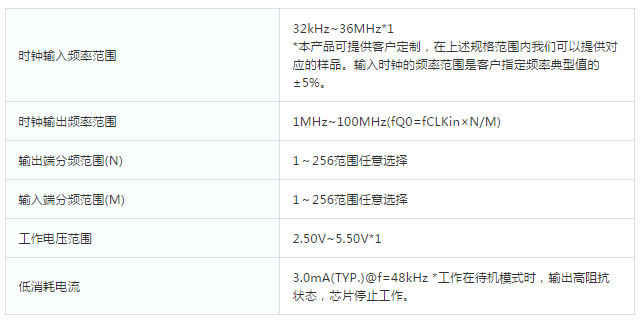

产品封装图 返回TOP

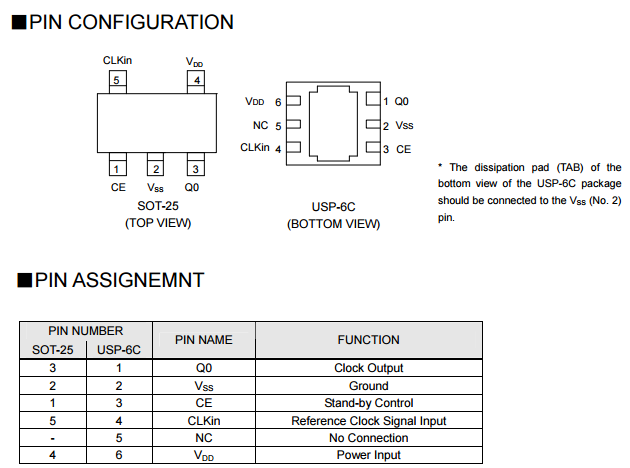

电路原理图 返回TOP

相关芯片选择指南 返回TOP 更多同类产品......

|

LL时钟发生器 |

|||||||

|

产品名称 |

特点 |

封装 |

电压范围(V) |

输出频率(MHz) |

消耗电流 (mA) |

||

|

MIN |

MAX |

MIN |

MAX |

||||

|

内置基频晶振电路PLL,对应高频 |

SOT-26 |

3 |

5 |

50 |

160 |

10 |

|

|

分頻因子:1.3~2047分頻倍 頻因子:6~2047倍頻 |

SOT-26 USP-6B |

2.97 |

5.5 |

3 |

30 |

3 |

|

|

输入端分频范围(M): 1~256分周, 输出端分频范围(N): 1~256分周 |

SOT-25 USP-6C |

2.5 |

5.5 |

1 |

100 |

3 |

|

|

输入端分频范围(M): 1~256分周, 输出端分频范围(N): 1~256分周 |

SOT-26W USP-6C |

2.5 |

5.5 |

1 |

100 |

5 |

|