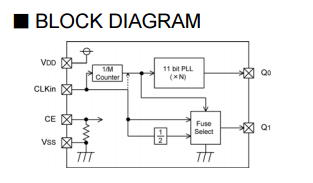

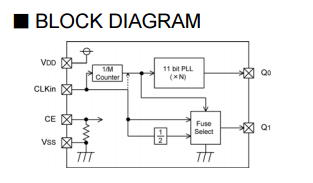

Output frequency (Q0) is equal to reference oscillation (fCLKin) multiplied by N/M, within a range of 3MHz to 30MHz. Q1 output is selectable from input reference frequency (f0), input reference frequency/2 (f0/2), ground (GND), and comparative frequency (f0/M). Further, comparative frequencies, within a range of 12KHz to 500KHz, can be obtained by dividing the reference oscillatio

-

[ CXCL3471BC5 ]"

目录

7.相关产品

产品概述 返回TOP

CXCL3471BC5系列是以高频, 低消耗电流工作,内置分频, 倍频电,路的超小型封装PLL时钟发生器。内置有分频电路, 倍频PLL电路。能够用微调技术从1,3~2047的分频因子(M),以及6~2047的倍频因子(N)中选择任意值。相对于主时钟(fCLKin)的输出频率Q0为:Q0=fCLKin×N//M。输出频率范围为3MHz~30MHz。Q1端的输出可从主时钟, GND, 比较频率/2, PLL输出频率/2中进行选择。对主时钟信号可输入14kHz~35MHz的基准时钟信号。将该主时钟分频,生成比较频率。比较频率范围为12kHz~500kHz。能够通过CE端停止振荡,减少消耗电流。此时,输出处于高阻抗状态。The CXCL3471BC5 series are high frequency, low power consumption PLL clock generator ICs with divider circuit & multiplier PLL circuit. Laser trimming gives the option of being able to select from divider ratios (M) of 1,3 to 2047 and multiplier ratios (N) of 6 to 2047. Output frequency (Q0) is equal to reference oscillation (fCLKin) multiplied by N/M, within a range of 3MHz to 30MHz. Q1 output is selectable from input reference frequency (f0), input reference frequency/2 (f0/2), ground (GND), and comparative frequency (f0/M). Further, comparative frequencies, within a range of 12KHz to 500KHz, can be obtained by dividing the reference oscillatio

产品特点 返回TOP

应用范围 返回TOP

●Crystal oscillation modules

●Personal computers

●PDAs

●Portable audio systems

●Various system clocks

技术规格书(产品PDF) 返回TOP

需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持!

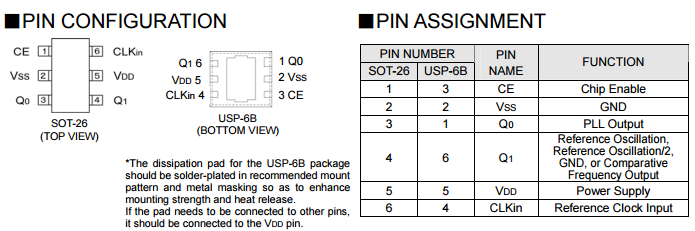

产品封装图 返回TOP

电路原理图 返回TOP

相关芯片选择指南 返回TOP 更多同类产品......

|

LL时钟发生器 |

|||||||

|

产品名称 |

特点 |

封装 |

电压范围(V) |

输出频率(MHz) |

消耗电流 (mA) |

||

|

MIN |

MAX |

MIN |

MAX |

||||

|

内置基频晶振电路PLL,对应高频 |

SOT-26 |

3 |

5 |

50 |

160 |

10 |

|

|

分頻因子:1.3~2047分頻倍 頻因子:6~2047倍頻 |

SOT-26 USP-6B |

2.97 |

5.5 |

3 |

30 |

3 |

|

|

输入端分频范围(M): 1~256分周, 输出端分频范围(N): 1~256分周 |

SOT-25 USP-6C |

2.5 |

5.5 |

1 |

100 |

3 |

|

|

输入端分频范围(M): 1~256分周, 输出端分频范围(N): 1~256分周 |

SOT-26W USP-6C |

2.5 |

5.5 |

1 |

100 |

5 |

|