The CXTP65155 is a high performance linear regulator designed to provide power for termination of a DDR memory bus. It significantly reduces parts count, board space and overall system cost over previous switching solutions. The CXTP65155 maintains a fast transient response using only 20μF or 30μF output capacitance. The CXTP65155 supports a remote sensing function and all power requirements for DDR, DDR2, DDR3 and Low Power DDR3/DDR4 VTT bus termination. The CXTP65155provides current and thermal limits to prevent damage to the linear regulator. Additionally, The CXTP65155generates an open-drain PGOOD signal to monitor the output regulation. An active high enable pin EN can pull VTT low, but REFOUT will remain active. A power savings advantage can be obtained in this mode through lower quiescent current.

-

[ CXTP65155 ]"

目录

7.相关产品

产品概述 返回TOP

CXTP65155是一款高性能的线性稳压器,能够做为DDR内存总线终端电源,和过去的开关解决方案比较,它显著的减少了器件数量,节省了板子的空间和系统成本。CXTP65155仅使用20μF or 30μF的输出电容就可以保持高速的瞬态响应。CXTP65155支持远程监测功能并满足所有DDR, DDR2, DDR3和低压的DDR3/DDR4 VTT总线终端电源的需求。CXTP65155具有过流和过温保护,另外,CXTP65155用漏极开路的PGOOD信号,监视输出的调整功能。当使能信号高有效时可以将VTT拉低,但是REFOUT还将保持有效,这是一种节能工作模式,在这种模式下,静态电流较低。CXTP65155有3mm x 3mm 的TDFN封装和SOP-8 (EP)封装。The CXTP65155 is a high performance linear regulator designed to provide power for termination of a DDR memory bus. It significantly reduces parts count, board space and overall system cost over previous switching solutions. The CXTP65155 maintains a fast transient response using only 20μF or 30μF output capacitance. The CXTP65155 supports a remote sensing function and all power requirements for DDR, DDR2, DDR3 and Low Power DDR3/DDR4 VTT bus termination. The CXTP65155provides current and thermal limits to prevent damage to the linear regulator. Additionally, The CXTP65155generates an open-drain PGOOD signal to monitor the output regulation. An active high enable pin EN can pull VTT low, but REFOUT will remain active. A power savings advantage can be obtained in this mode through lower quiescent current. The CXTP65155is available in the 3mm × 3mm TDFN-10 and SOP-8 (EP) packages.

产品特点 返回TOP

• VLDOIN输入电压范围:1.1-3.5 V

• VIN输入电压范围: 2.375V to 5.5V

• 典型DDR应用时需要三个10μF 的MLCC电容

• 快速负载瞬态响应

• ±10mA缓冲基准电压(REFOUT)

• 符合DDR, DDR2 JEDEC的规格

• 支持DDR3和低压的DDR3/DDR4 VTT应用

• Power-Good窗口比较器

• 软启动,欠压,过流保护

• 热关断功能

• 3mm x 3mm TDFN 封装和SOP-8 (EP)封装

• 符合RoHS标准,100%无铅和无卤素

z VLDOIN Input Voltage Range: 1.1V to 3.5V

z VIN Input Voltage Range: 2.375V to 5.5V

z Typically 3×10μF MLCCs stable for DDR

z Fast Load-Transient Response

z ±10mA Buffered Reference (REFOUT)

z Meet DDR, DDR2 JEDEC Specifications. Supports DDR3 and Low-Power DDR3/DDR4 VTT Applications

z Power-Good Window Comparator

z With Soft Start, UVLO and OCP

z Thermal Shutdown

z Available in 10-Pin 3mm×3mm TDFN and SOP-8 (EP) packages

z RoHS Compliant and 100% Lead(Pb)-Free Halogen-Free

应用范围 返回TOP

• 笔记本,台式机和服务器

• DDR内存终端

• 电信,GSM基站,LCD-TV/PDP-TV,复印机,机顶盒Notebook/Desktop/Server

z DDR Memory Termination

z Telecom/Datacom, GSM Base Station, LCD-TV/PDP-TV, Copier/Printer, Set-Top Box

技术规格书(产品PDF) 返回TOP

需要详细的PDF规格书请扫一扫微信联系我们,还可以获得免费样品以及技术支持!

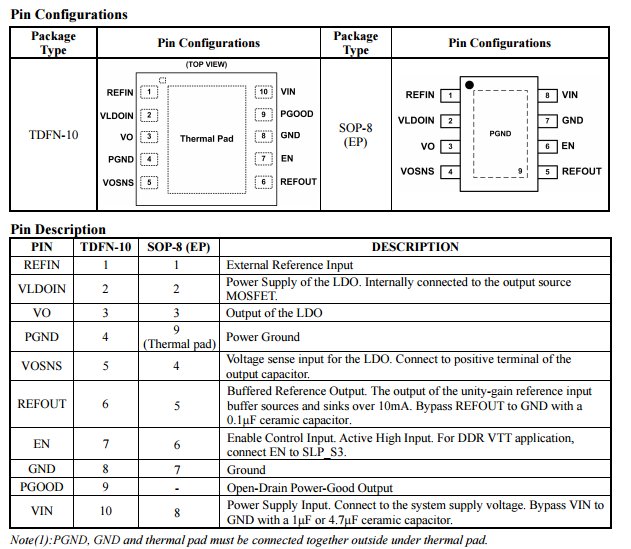

产品封装图 返回TOP

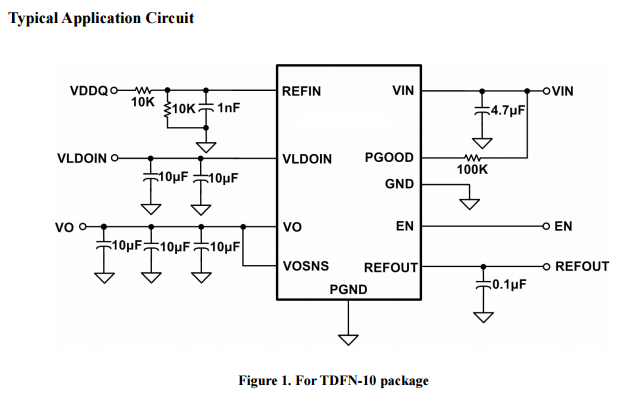

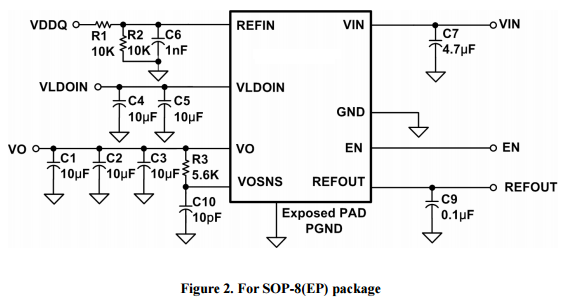

电路原理图 返回TOP

相关芯片选择指南 返回TOP 更多同类产品......

|

DDR终端稳压器 |

|||||||

|

Part Number |

remark |

Iout (A) |

Vin (V) |

Vout (V) |

Output Voltage Accuracy (mV) |

Shutdown |

Package |

|

1.5A DDR Termination Regulator |

± 1.5 |

1.8 ~ 5.5 |

0.9~1.25 |

± 20 |

Yes |

SOP-8 (EP) |

|

|

2A Sink/Source Bus Termination Regulator |

± 2 |

1.8 ~ 5.5 |

0.9~1.25 |

± 20 |

Yes |

SOP-8 (EP) |

|

|

Sink/Source DDR Termination Regulator |

± 2 |

2.375 ~ 5.5 |

0.5~1.8 |

± 25 |

Yes |

TDFN-10,SOP-8 |

|

|

DDR Termination Regulator |

± 1.5 |

1.5~3.3 |

0.75~0.9 |

±20 |

Yes |

SOP-8(EP) |

|